The Top level module in test bench must be the name of the entity of your testbench file. This name will later appear in the Compile test bench list. Notice the directly instantiated entity is specified with a selected name specifying the library the entity is found in. The Test bench name can be any suitable name by your choice. Also, add the provided testbench countertb.vhd.

vho file with the same name as your project.

Modelsim altera tutoral testbench code#

That way someone reading the code doesn't have to count arguments while looking somewhere else. First, in your Quartus project directory, there should be a simulation/modelsim directory. It's generally useful to have a valid component declaration or to at least use formal association (instead of positional, the above shows formal). library ieee Īrchitecture test of quarter_round_vhd_tst isīut the component declaration still needs to match the entity declaration for quarter_round.Īnd if you're sure you'll never need to configure quarter_round in the testbench you can use direct entity instantiation, eliminating the component declaration: - component quarter_round Note the type in the component declaration and the entity quarter_round don't match. So the problem you describe after the edit shows up during elaboration. Signal interface "z" from component "quarter_round" and port "z" fromĮntity "quarter_round" are not compatible for an association ghdl: "quarter_round" and port "y" from entity "quarter_round" are notĬompatible for an association quarter_round.vhdl:100:1: type of

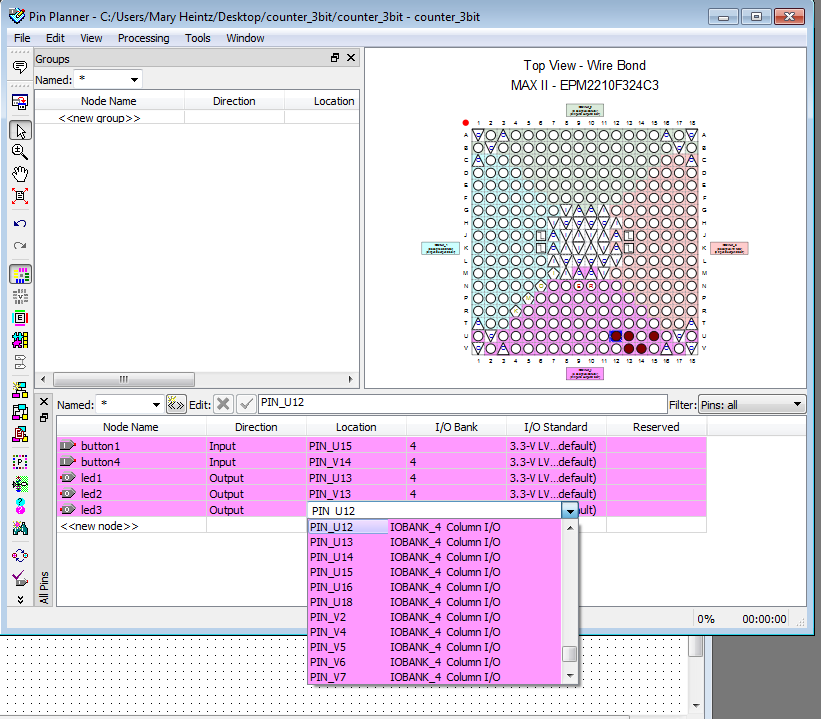

Quarter_round.vhdl:100:1: type of signal interface "y" from component Go to Assignments -> Settings and select Modelsim-Altera in the Tool. Code is compiling but Modelsim giving errors saying types do not match. In this tutorial, we will program the DE-nano board, to be a simple 3 bit counter. Signal z0,z1,z2,z3 :unsigned( 31 downto 0) Signal j1,j2,j3,j4 :unsigned( 31 downto 0) Signal i1,i2,i3,i4 :unsigned( 31 downto 0) Invoke ModelSim-Altera and compile design files: a. You can then perform an RTL or gate-level simulation to verify the correctness of your design. The code for the Quarterround (which is top level): LIBRARY ieee ĪRCHITECTURE quarter_round_arch of quarter_round is Creating Testbench using ModelSim-Altera Wave Editor You can use ModelSim-Altera Wave Editor to draw your test input waveforms and generate a Verilog HDL or VHDL testbench. All attempts I've made have resulted in the output, z, not giving any values. I understand I have to 'stimulate' the inputs to observe the outputs. I want to test it in Modelsim before moving on but I am encountering difficulties. Its main function is the 'quarterround' which I have successfully written. I'm in the process of writing the VHDL code for Salsa20 stream cipher.

0 kommentar(er)

0 kommentar(er)